Aujourd’hui, la grande majorité de la mémoire utilisée par les ordinateurs de bureau, les ordinateurs portables et les appareils mobiles est de la DRAM non ECC (Error Checking and Correction) non tamponnée. En fait, à moins d’utiliser un processeur Intel ou AMD qui peut prendre en charge la mémoire ECC, la DRAM ECC non tamponnée est le seul choix pour la plupart des utilisateurs. Les Intel Xeons, par exemple, prennent en charge la mémoire ECC, alors que même les nouveaux Core i7 ne le font pas. AMD a un support ECC beaucoup plus large au niveau du processeur, mais de nombreuses cartes mères AMD ne supportent pas les fonctionnalités de la mémoire ECC, donc ce n’est pas universel.

La mémoire ECC ce qu’elle fait

La mémoire de vérification et de correction des erreurs (ECC) est surtout considérée comme essentielle dans les environnements d’entreprise de nos jours. La vérification et la correction des erreurs sur un seul bit dans un octet de 8 bits permet de détecter et de corriger les erreurs sur un seul bit lorsqu’elles se produisent. Il est intéressant de noter que le fonctionnement de l’ECC sur un seul bit n’est pas si différent de celui du RAID 4 et du RAID 5, où un algorithme XOR est utilisé pour générer des bits de parité. Au lieu de perdre de la capacité de mémoire utilisable, les fabricants de mémoire ont tendance à ajouter une puce supplémentaire à la mémoire ECC pour chaque huit puces de stockage. Lorsqu’une erreur d’un seul bit est détectée, les informations de parité sont utilisées pour reconstruire les données comportant une erreur. Là encore, le concept est similaire à la façon dont les systèmes RAID 4 et RAID 5 peuvent épurer et réparer les erreurs de données dans les matrices de stockage. Les erreurs plus importantes que les multi-bits peuvent être détectées mais pas corrigées par le type de parité ECC à un seul bit.

Pour les ordinateurs de bureau, cela est moins important car beaucoup de chiffres placent les erreurs à un seul bit dans la gamme de 1 pour 1 Go ou 1 pour 2 Go de mémoire chaque mois. Pour un utilisateur d’ordinateur de bureau, cela peut provoquer le plantage d’un programme ou, au pire, nécessiter un redémarrage. Dans les serveurs, l’ECC est essentiel pour maintenir l’intégrité des données et le temps de fonctionnement. Avec le différentiel de coût mineur actuel des DIMM ECC par rapport aux DIMM non ECC non tamponnés, il y a peu de raisons d’obtenir de la mémoire non ECC pour un serveur.

Mémoire ECC non tamponnée contre mémoire ECC enregistrée

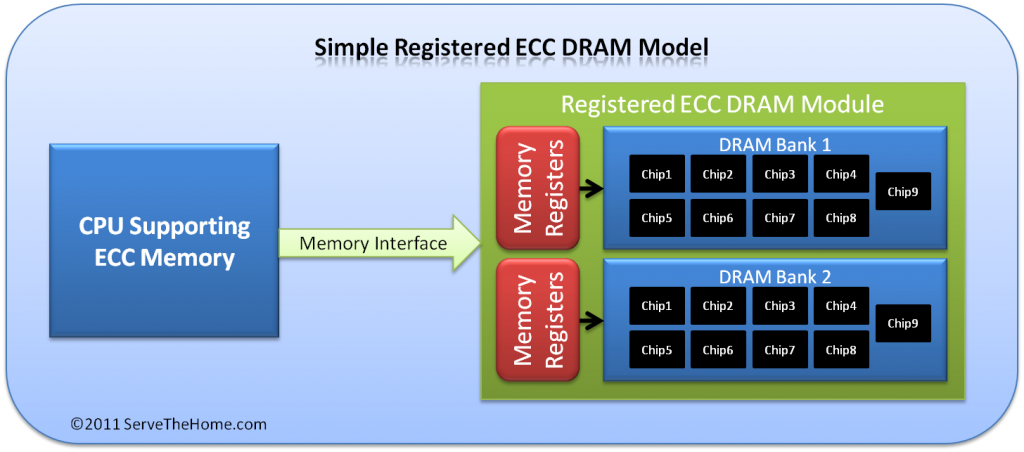

Ajoutant au concept ECC, il y a deux concepts en jeu, les modules de mémoire ECC non tamponnés et enregistrés. La différence fondamentale est que les commandes de mémoire dans les configurations de mémoire non tamponnée vont directement du contrôleur au module de mémoire, tandis que dans les configurations de mémoire enregistrée, les commandes sont d’abord envoyées aux registres des banques de mémoire avant d’être envoyées aux modules. Ce concept peut sembler difficile, mais voici la vue très simple/conceptuelle concernant ce qui se passe.

Dans l’exemple ci-dessus, le contrôleur de mémoire accède directement aux banques de mémoire. Ce qui précède suppose que le contrôleur de mémoire réside dans le boîtier du CPU, comme c’est le cas dans les architectures de CPU modernes. En regardant les systèmes plus anciens, le contrôleur de mémoire résidait dans le northbridge du CPU. Comparez cela à l’exemple de mémoire enregistrée ci-dessous.

Ici, le CPU communique avec les registres des banques de mémoire sur chaque module. De là, ces registres communiquent avec la DRAM. Les implications de ceci sont doubles. Tout d’abord, d’un point de vue négatif, les instructions prennent environ un cycle CPU de plus en raison de l’intermédiaire du registre de banque. D’un point de vue positif, cette mise en mémoire tampon réduit la pression exercée sur le contrôleur de mémoire du CPU, car il pointe vers le registre intermédiaire dédié au lieu d’accéder directement à la DRAM. Il est plus facile pour le contrôleur de mémoire de traiter un nombre moins important de cibles.

Cette fonctionnalité est très importante dans les scénarios de serveur car, par exemple, une plateforme de la série Intel 3400, comme le Supermicro X8SI6-F ou l’Intel S3420GPLC prend en charge 16 Go de mémoire ECC non tamponnée et 32 Go de mémoire ECC enregistrée. De même, dans les systèmes à double processeur, tels que le Supermicro X8DTH-6F basé sur la série E5600, récemment examiné sur ServeTheHome, le delta est beaucoup plus grand avec jusqu’à 48 Go de mémoire ECC non enregistrée ou 192 Go de mémoire ECC enregistrée. Pour les environnements de virtualisation où la mémoire et la bande passante de la mémoire sont essentielles pour obtenir des mesures de consolidation et de densité élevées, la mémoire ECC enregistrée est généralement la voie à suivre. Si l’on achète un serveur avec des DIMM ECC non enregistrés, puis que l’on a besoin d’une capacité supplémentaire, alors l’opération de mise à niveau nécessitera de tirer et de remplacer tous les modules UDIMM, ce qui en fait une proposition coûteuse.

Conclusion

Dans cet article, on espère pouvoir obtenir une vue conceptuelle de la différence entre la mémoire ECC non tamponnée et la mémoire ECC enregistrée pour aider à éclairer les décisions de sélection. Ce n’était pas un article trop technique parce que les modules de mémoire ont tendance à être des éléments que les gens commandent avec ou ajoutent à leurs systèmes et font peu de travail sur jusqu’à ce qu’ils aient besoin de plus de mémoire.